Le 8008 d'Intel est un processeur assez particulier. C'est le premier micro-processeur 8 bits, et on peut même dire : le premier micro-processeur tout court. Son grand frère, le 4004, étant plutôt considéré comme un micro-contrôleur. D'autres sites expliquent le pourquoi de cette distinction.

Je veux ici me pencher sur le 8008 sous certains aspects techniques. Une brève introduction d'une puce qui va en générer d'autres (8080, 8086, Z80,...)

Cette puce, je l'ai étudiée à travers son utilisation dans le Micral N de la R2E, mais ceci est une autre histoire. Le 8008 est rapidement utilisé dans une série de micro-ordinateurs (le terme apparaît avec le Micral N) sur un cours laps de temps. Dans le désordre, MCM/70, SCELBI, Intellec-8, Mark-8, MCS 8, Bill-1,... Certaines de ces machines reçoivent très rapidement une mise à jour vers le 8080, beaucoup plus flexible. Cependant, c'est bien avec le 8008 que cela commence.

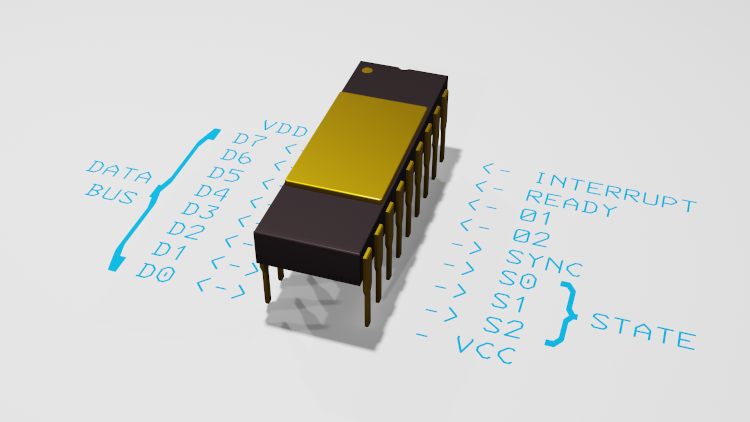

La puce

Et le voici en image de synthèse. Ou du moins, dans l'un des boîtiers existant, car il en existe plusieurs. C'est celui que j'avais en référence, et c'est donc celui que j'ai modélisé.

Une première chose étonnante : pas de masse. Le 8008 prend du +5V et du -9V. Il semble que la raison soit une volonté d'être compatible avec des circuits électroniques 5V, mais avec un besoin d'une tension totale de 14V... Ce n'est pas trop mon rayon, alors je laisse ça en note. Pour plus de précisions, jusqu'au niveau transistor, je vous dirige vers l'analyse en anglais de Ken Shirriff.

Branchements

Mis à part VCC et VDD, les deux tensions nécessaires, le 8008 communique avec l'extérieur à travers 16 autres broches.

À noter que le 8008 travaille en « logique physique inversée » par rapport aux signaux logiques : le 0 logique est à +5V, le 1 logique est entre ~0.8V et -9V.

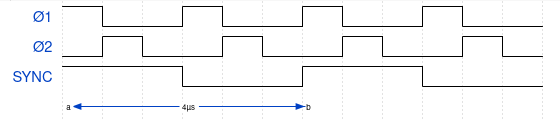

Broche de synchronisation

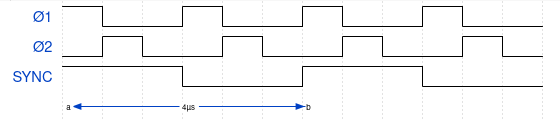

En entrée, le 8008 reçoit en entrée deux horloges déphasées, de même fréquence (500 kHz) : Ø1 et Ø2. Ces deux horloges lui permettent de cadencer les opérations internes.

À partir de ces impulsions, le 8008 forme en sortie le signal SYNC/ qui est haut pendant un premier cycle Ø1, Ø2, puis bas pendant un second cycle Ø1, Ø2. Le tout forme un état processeur complet.

Vu qu'il y a un temps de 2µs entre deux fronts de Ø1, cela signifie qu'un état du 8008 dure 4µs.

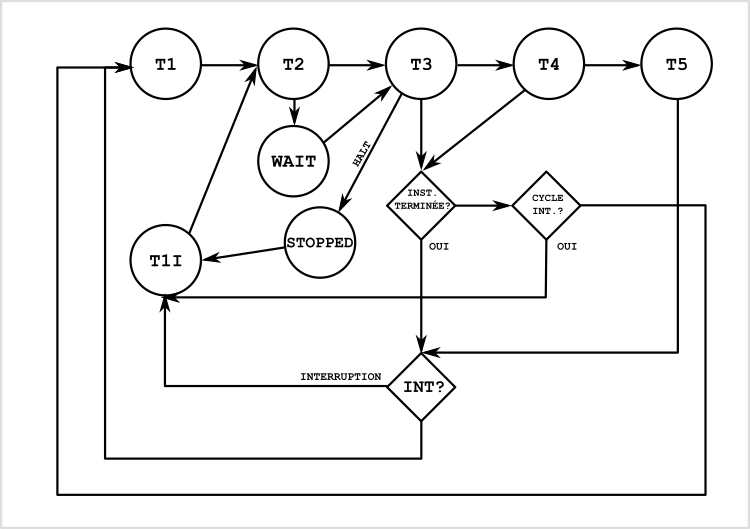

Broches d'états

Trois autres broches en sortie : S1, S2 et S3, forment un triplet indiquant dans quel état le processeur se trouve.

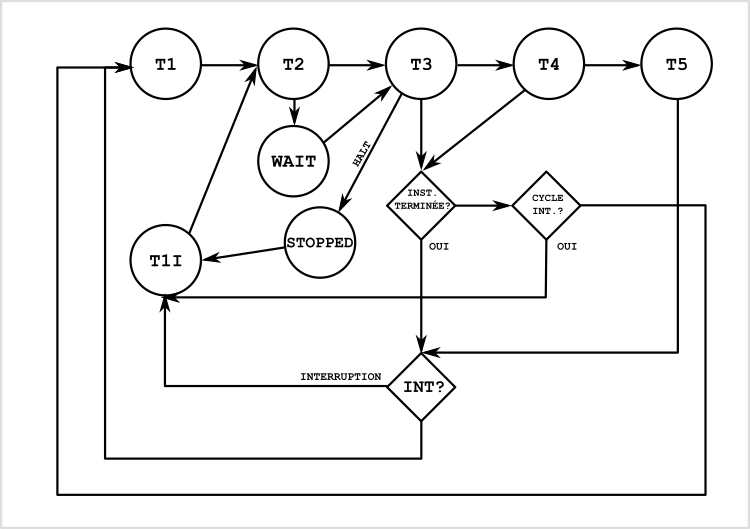

Les états sont les suivants : T1 et T1I, T2, T3, T4, T5, WAIT et STOPPED.

Les états T1 et T2 forment ensemble une demande d'information au reste du système. Lors de T1, le 8008 place la partie basse de l'adresse de l'information à obtenir sur les broches d'entrées/sorties. Lors de T2 y est placée la partie haute de l'adresse, ainsi que deux bits indiquant le type de cycle actuel et donc la nature de la donnée attendue : est-ce une instruction, une lecture ou une écriture de donnée en mémoire, ou une opération d'entrée/sortie ?

Cette manière de placer une adresse sur le bus se fera toujours de la même manière lors de différents cycles d'une instruction, et toujours sur les états T1 et T2 : d'abord les 8 bits bas de l'adresse, puis les 6 bits haut (le 8008 a un espace d'adressage de 14 bits), complétés par 2 bits indiquant au système ce que ce couple d'information représente.

T1I est une variante de T1 qui est utilisée lorsque le processeur a validé une interruption. L'état est le même que T1 à l'exception du traitement du compteur d'instruction (le registre interne PC), qui n'est pas avancé. Après T1I, le 8008 passera à un état T2.

Lors de l'état T3, le processeur lit la donnée obtenue. Si c'est une instruction à exécuter, celle-ci est stockée pour les états suivants, sauf pour l'instruction HLT, qui est immédiate.

Les états T4 et T5 sont des états supplémentaires qui existent dans certaines instructions.

Et chaque instruction peut répéter l'ensemble de ces états dans l'ordre pour compléter son exécution. L'instruction INr (incrément d'un registre) va s'exécuter en un seul cycle avec les états T1, T2, T3, T4 et T5, pour un total de 5 états. L'instruction JMP (branchement à une adresse absolue) aura besoin de trois cycles : le premier et le second avec T1, T2 et T3, le troisième avec T1, T2, T3, T4 et T5, pour un total de 11 états.

Broches d'entrée

Le 8008 possède deux broches en entrée en plus des deux phases d'horloges : INTERRUPT/ et READY/.

READY/

La broche READY/ permet de synchroniser le temps que prend l'acquisition d'une donnée avec le 8008. En effet, le cycle T3 s'attend à pouvoir lire une donnée sur les broches d'entrées/sorties. L'emplacement de cette donnée a été complètement caractérisée (emplacement et nature) lors du cycle T2.

Pour être certain que le monde extérieur est prêt, le 8008 ne passera de l'état T2 à T3 que si READY/ est au 1 logique. Dans le cas contraire, il se placera dans l'état WAIT et patientera... Dès que READY/ est signalé par le reste du système, le 8008 reprend sa course en passant vers l'état T3.

INTERRUPT/

La broche INTERRUPT/, comme son nom l'indique, place le 8008 dans un état d'interruption. La gestion des interruptions par le 8008 est très rudimentaire. Lorsqu'une instruction est terminée, si INTERRUPT/ est signalée, alors le processeur passe en état T1I plutôt que T1.

Et c'est tout !

C'est aussi le seul moyen pour le processeur de sortir de l'état STOPPED si une instruction HLT (halt) a été exécutée. Et de la même manière, le premier état sera alors T1I.

Comme indiquée plus haut, la différence entre l'état T1 et T1I est que pour T1, le registre PC est incrémenté après l'émission de l'adresse. Pas dans le cas de T1I. L'idée est pour le système de placer sur le bus lors d'un état T1I une instruction particulière, généralement RST (Restart).

L'instruction RST est une instruction d'un octet de taille qui permet de brancher sur une sous-routine (comme un CAL) à une des 8 adresses multiples de 8 en mémoire. Elle est faite pour être utilisée dans ce contexte.

Le 8008 doit donc être aidé par le reste du système pour gérer des interruptions. Le processeur lui-même ne fait que le strict minimum...

Les broches d'entrées/sorties

Il reste 8 broches à décrire, et celles-ci fonctionnent en entrée comme en sortie. Elles forment l'interface d'échange de données entre le 8008 et le reste du système. Ces broches ne sont pas spécialisées : toute donnée passe par là, que ce soit un morceau d'adresse, une données à échanger avec la mémoire ou avec un périphérique.

Comme indiqué plus haut, une combinaison de l'état courant du 8008 et des deux bits hauts placés en T2 sur ces broches permet de déterminer la fonction de ces 8 broches.

Sur T1 et T2, ce sont des broches en sortie qui indiquent deux morceaux d'adresse ainsi que la nature du cycle. Sauf dans le cas d'une données adressée à un périphérique, qui se trouvera en cycle T1 du second cycle.

En T3, ce sont des broches en entrée qui vont y lire une donnée... ou rien (dans le cas de OUT lors du second cycle).

Les broches ne servent pas lors des autres états.

Les registres

Le 8008 possède des registres accessibles par le code utilisateur, ainsi que quelques registres internes, non accessibles.

Passons sur la plupart des registres internes, qui servent au fonctionnement... interne (deux registres temporaires, celui d'instruction, de cycle,...) mais arrêtons nous sur une particularité : le pointeur d'instruction, généralement nommé PC sur les micro-processeurs, n'est pas accessible au code exécuté !

Le PC

En premier lieu, il faut dire que ce registre n'existe pas vraiment. Le 8008 possède une mémoire de 8 x 14 bits organisée en pile, munie de son pointeur de pile. L'adresse pointée est le PC actuel. Lors d'un branchement, l'adresse pointée est mise à jour, avec une mise à jour potentielle du pointeur dans le cas d'instruction d'appel de sous-routine (CAL par exemple).

Cela signifie au passage que le 8008, sans aide externe et avec ses seules instructions, ne peut pas dépasser une profondeur d'appel de plus de 8. Ou plutôt, il peut, mais la mémoire étant cyclique, il ne pourra pas remonter correctement.

Et le contenu de cette mémoire est parfaitement inaccessible. Il n'y a pas d'instruction permettant de lire le contenu de la pile, ni le niveau du pointeur.

Les autres registres

Les registres accessibles sont A, B, C, D, E, H et L. Rien de très étonnant si vous connaissez le Z80 par exemple.

A est l'accumulateur. Toutes les opérations logiques et arithmétiques se font par rapport à A, et le résultat potentiel est stocké dans A. Sauf pour les opérations d'incréments et décréments, qui ne peuvent être appliqués que sur les registres généraux qui suivent.

B, C, D et E sont 4 registres généraux. On peut copier le contenu de n'importe lequel vers n'importe quel autre (y compris l'accumulateur). On peut même copier le contenu d'un registre vers lui-même. Et c'est d'ailleurs, par convention, la copie de A vers A (LAA) qui forme l'instruction NOP du 8008.

H et L sont 2 autres registres généraux qui se comportent comme les précédents, mais qui ont une capacité supplémentaire. Pris ensemble, ils forme HL, nommé aussi M, un pseudo registre de pointeur vers la mémoire.

Ainsi, l'instruction LAM copie le contenu du pseudo registre M vers l'accumulateur. Autrement dit, l'octet pointé par la paire HL est chargée dans A.

Mot de la fin.

Le 8008, conçu et construit par Intel, est avant tout une commande pour reproduire dans un petit volume les fonctionnalités d'un appareil existant. C'est sous cet aspect qu'il est à comprendre et comprendre une partie des choix techniques et donc de ses limitations.